Multiple PLC technologies to be bridged to form very large networks. Important benefits of being able to easily interface with traditional binary logic circuits. Quaternary radix offers all the advantage of MVL such as minimization of area due to signal routing reduction along with the Quaternary logic (radix-4-valued) is chosen as the base radix for the work reported here. Several approaches for quaternary circuit design have been proposed, in voltage mode technique. Mode circuits provide lesser power consumption which has been the key advantage of traditional CMOS binary logic circuitsįrom the perspective of dynamic switching procedure.

Inherent nature of constant current flow during the operation.Īlternatively, voltage-mode circuits exhaust a large majority of power only during the logic level switching. They can fundamentally classified as current-mode, voltage-mode and mixed-modeĬircuits current-mode circuits have been popular and offer several benefits, the power consumption is high due to their Latest papers to realize the MVL circuits.

Number of implementation methods has been proposed in the Increased data density, optimize dynamic power dissipation, and increased computational ability areĪmong some of the key benefits of Multiple Valued Logic (MVL). Today’s four value logic which we called quaternary

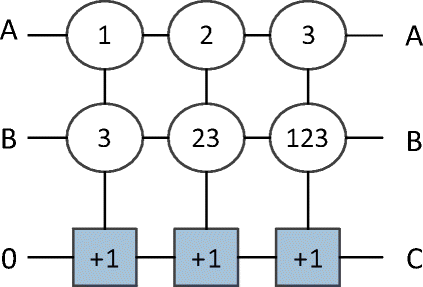

Only two possible values for any proposition true and (1’s or 0’s) that is in the form of. Multiple value logic is logical calculi which contain more than two possible truth values. Keywords: Half Adder, Full Adder, Multi Value Logic, Complementary Metal-Oxide Semiconductor We try to find area, power and speed of the design HAq / FAq without any need of conversion, and compare to existing binary Circuit is design by using Advanced Design System software. The design is targeted for the 0.18 μm CMOS technology. Addition operation is executed with minimum number of gates and less depth of net. In quaternary half adder, quaternary logic levels are exploited for the intention of addition. The presented adders are design in Multiple-Valued voltage-Mode Logic (MV-VML). Multiple-valued logic (MVL) designs are gaining more advantageous from the design of a multiple-valued half adder and full adder circuits. This technique advantageous for large scale circuits due to which large power dissipation with increased speed can lead to the development of extremely low energy circuit’s use for the high performance required for number of applications. This paper gives the fabrication of a multiple-valued half adder and full adder circuits. Multiple-valued logic (MVL) designs contain more importance from that perspective. This difficulty overcomes by using a big set of signals over the same chip area. The digital logic circuits are restricted for the requirement of interconnections.

0 kommentar(er)

0 kommentar(er)